Un grupo de investigadores del Instituto de Tecnología de Massachusetts (MIT) ha desarrollado un chip de bajo consumo de energía capaz de evitar que los hackers extraigan información oculta de los dispositivos inteligentes a través de un ataque de canal lateral, garantizando así una mayor protección de datos.

Un ataque de canal lateral busca recopilar información secreta explotando indirectamente un sistema o su hardware. En un tipo de ataque de canal lateral, un hacker podría monitorear las fluctuaciones en el consumo de energía del dispositivo mientras la red neuronal está operando para extraer información protegida que se ‘filtra’ fuera del dispositivo.

Los métodos actuales que pueden prevenir algunos ataques de canal lateral son notoriamente intensivos en energía, por lo que a menudo no son factibles para dispositivos de IoT que dependen de un cálculo de baja potencia.

Cálculo de umbral

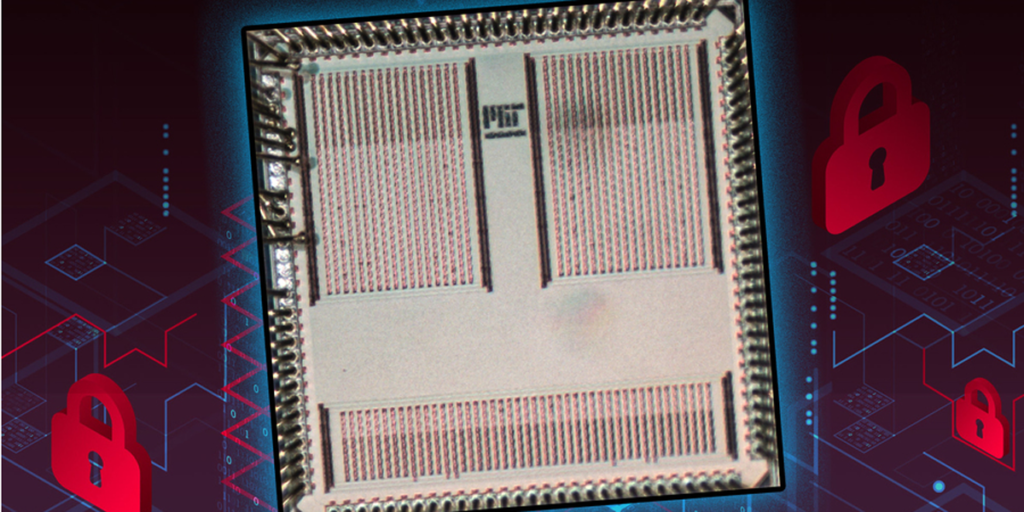

Para solucionar este problema, los investigadores del MIT han creado un chip de circuito integrado que puede defenderse contra los ataques de canal lateral de energía, mediante el uso de menos energía que la técnica de seguridad común. El chip, más pequeño que una miniatura, podría incorporarse en el dispositivo inteligente para realizar cálculos seguros de aprendizaje automático con los valores del sensor.

El chip se basa en un tipo especial de cálculo conocido como cálculo de umbral. En lugar de que una red neuronal opere con datos reales, los datos primero se dividen en componentes únicos y aleatorios. La red opera en esos componentes aleatorios individualmente, en un orden aleatorio, antes de acumular el resultado final.

Con este método, la fuga de información del dispositivo es aleatoria cada vez, por lo que no revela ninguna información real del canal lateral. Sin embargo, este enfoque es más costoso desde el punto de vista computacional, ya que la red neuronal ahora debe ejecutar más operaciones y también requiere más memoria para almacenar la información desordenada.

Por ello, los investigadores optimizaron el proceso mediante el uso de una función que reduce la cantidad de multiplicación que necesita la red neuronal para procesar los datos, lo que disminuye drásticamente la potencia informática requerida. También protegen la propia red neutral cifrando los parámetros del modelo. Al agrupar los parámetros en fragmentos antes de cifrarlos, brindan más seguridad y reducen la cantidad de memoria necesaria en el chip.

Método de computación optimizado

Los métodos de computación seguros existentes, como el cifrado homomórfico, ofrecen garantías sólidas de seguridad, pero incurren en enormes gastos generales en área y energía, lo que limita su uso en muchas aplicaciones. El método propuesto por los investigadores pudo lograr un uso de energía tres órdenes de magnitud menor. Al optimizar la arquitectura del chip, los investigadores también pudieron usar menos espacio en un chip de silicio que en un hardware de seguridad similar.

Para verificar su eficacia en la protección de datos, los investigadores compararon el nuevo chip con una implementación predeterminada que no tenía hardware de seguridad. En la implementación predeterminada, pudieron recuperar información oculta después de recopilar alrededor de 1.000 formas de onda de energía (representaciones del uso de energía a lo largo del tiempo) del dispositivo. Con el nuevo hardware, incluso después de recolectar 2 millones de formas de onda, aún no pudieron recuperar los datos.