Los ingenieros de la Universidad de Pensilvania (Filadelfia, EE.UU.) han desarrollado un chip escalable capaz de clasificar y reconocer imágenes casi instantáneamente, gracias a la eliminación de cuatro factores que consumen mucho tiempo en los chips de computadora tradicional: la conversión de señales ópticas en eléctricas, la necesidad para convertir los datos de entrada a formato binario, un módulo de memoria grande y cálculos basados en reloj.

Si bien la tecnología actual de clasificación de imágenes para el consumidor en un chip digital puede realizar miles de millones de cálculos por segundo, lo que la hace lo suficientemente rápida para la mayoría de las aplicaciones, una clasificación de imágenes más sofisticada, como la identificación de objetos en movimiento, la identificación de objetos en 3D o la clasificación de células microscópicas en el cuerpo, están empujando los límites computacionales, incluso de la tecnología más potente.

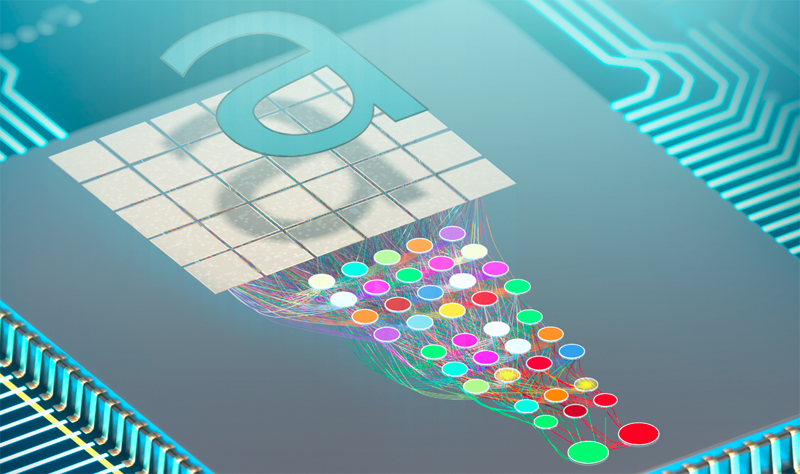

El límite de velocidad actual de estas tecnologías está establecido por el cronograma de pasos de cómputo basado en el reloj de un procesador de computadora, donde los cómputos ocurren uno tras otro en un cronograma lineal. Para eliminar este proceso, los investigadores incorporaron en un chip de 9,3 milímetros cuadrados una red neuronal profunda óptica, que lleva a cabo un procesamiento directo de la luz recibida del objeto de interés.

Red neuronal PDNN

El estudio, publicado en Nature, describe cómo las muchas neuronas ópticas del chip están interconectadas mediante cables ópticos o guías de ondas para formar una red profunda de muchas capas de neuronas, que imitan la del cerebro humano, creando una red neuronal profunda fotónica integrada de extremo a extremo (PDNN).

La información pasa a través de las capas de la red PDNN, que se encarga de realizar la clasificación de las imágenes en subnanosegundos mediante el procesamiento directo de las ondas ópticas que inciden en la matriz de píxeles en el chip a medida que se propagan a través de las capas de neuronas.

En cada neurona, el cómputo lineal se realiza de forma óptica y la función de activación no lineal se realiza de forma optoelectrónica, lo que permite un tiempo de clasificación inferior a 570 ps, que es comparable con un solo ciclo de reloj de las plataformas digitales de última generación.