Los investigadores del Instituto de Tecnología de Tokio (Tokyo Tech) han desarrollado un nuevo diseño de transceptor capaz de transmitir y recibir a frecuencias superiores a 100 GHz y a una velocidad de datos de 112 Gb/s. Esto ha sido posible al suprimir la autointerferencia causada por la fuga de la señal de transmisión en el receptor. Este dispositivo podría allanar el camino hacia las tecnologías 6G.

Científicos e ingenieros en el campo de las telecomunicaciones ya están trabajando en las tecnologías que se utilizarán para las redes de sexta generación (6G), que intenta ofrecer velocidades de datos de más de 100 Gb/s y admitir latencias extremadamente bajas para aplicaciones como automóviles autónomos y realidad virtual. Una forma de cumplir con estos requisitos masivos de transmisión y recepción es adoptar una arquitectura de dúplex completo (FD) que opere en frecuencias inferiores a THz de 88 a 136 GHz.

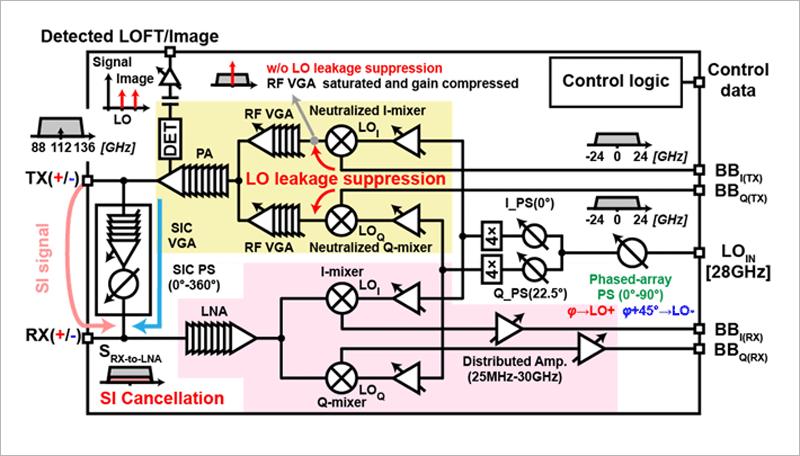

La principal ventaja de la arquitectura FD es que permite que un solo sistema transmita y reciba señales, duplicando efectivamente el rendimiento. Una forma de implementar esta arquitectura es hacer que los módulos de transmisión y recepción compartan una sola antena. Esto ayuda a reducir el tamaño del circuito y permite que ambas partes aprovechen al máximo el espectro de frecuencia disponible. Sin embargo, las arquitecturas FD de antena única sufren mucho de autointerferencia (SI), un fenómeno en el que la señal transmitida se filtra hacia el lado del receptor.

En este contexto, el equipo de Tokyo Tech ha desarrollado un sistema de comunicación FD que aborda los obstáculos que plantea la autointerferencia. Una de las principales características de su sistema es la implementación de una antena de parche de doble polarización, impulsada por señales diferenciales, una combinación de puertos de alimentación positivos y negativos para transmisión y recepción.

Al hacer que las rutas de los circuitos de estos puertos sean altamente simétricas, se minimiza la falta de coincidencia de la señal transmitida que se filtra hacia los puertos del receptor diferencial, lo que ayuda a mantener la autointerferencia baja.

Circuito de cancelación de la autointerferencia

Otro aspecto importante del diseño propuesto es el circuito de cancelación de la autointerferencia (SIC). Para cancelar efectivamente el SI generado, se necesita modificar cuidadosamente la fase de la señal de cancelación para que sea opuesta a la de la señal filtrada. Esto generalmente se hace usando capacitores variables llamados varactores.

Sin embargo, en el rango de sub-THz, los varactores convencionales tienen un rango de fase limitado y una resolución deficiente. Para abordar este problema, los investigadores desarrollaron una nueva estructura de varactor que logró una excelente resolución lineal en toda la banda de sub-THz y en el rango completo de 360°.

El equipo probó su diseño a través de una serie de experimentos, cuyos resultados eran bastante prometedores. El dispositivo funcionó a más de 100 GHz y alcanzó una velocidad de datos de 112 Gb/s en modo HD. Este es el sistema más rápido hasta la fecha entre los transceptores de matriz en fase sub-THz. Junto con un tamaño compacto y una amplia gama de frecuencias operativas, la arquitectura propuesta representa un gran paso hacia la tecnología de telecomunicaciones para 6G.