Un equipo de investigadores de la Universidad de Ciencia y Tecnología de China (USTC) de la Academia de Ciencias de China (CAS) diseñó un chip con un bucle de bloqueo de fase totalmente digital de onda milimétrica de baja fluctuación para mejorar las comunicaciones 5G/6G.

El chip CSS-ADPLL está basado en una innovadora técnica de muestreo de dirección de carga (CSS), que logra un rendimiento de fluctuación ultrabaja para aplicaciones de ondas milimétricas.

El chip sintetizador de frecuencia de ondas milimétricas de baja fluctuación, que sirve como un componente vital para permitir las comunicaciones de ondas milimétricas 5G/6G, ofrece señales portadoras precisas para los sistemas de comunicación de ondas milimétricas.

En este estudio, el equipo de investigación combinó el muestreo de dirección de carga con un convertidor de analógico a digital de tipo registro de aproximación sucesiva (SAR-ADC) utilizando la técnica de muestreo de timón de carga. Este enfoque permitió la construcción de un discriminador de fase digital con una ganancia de identificación de fase excepcional, alta linealidad y salidas digitales de múltiples bits.

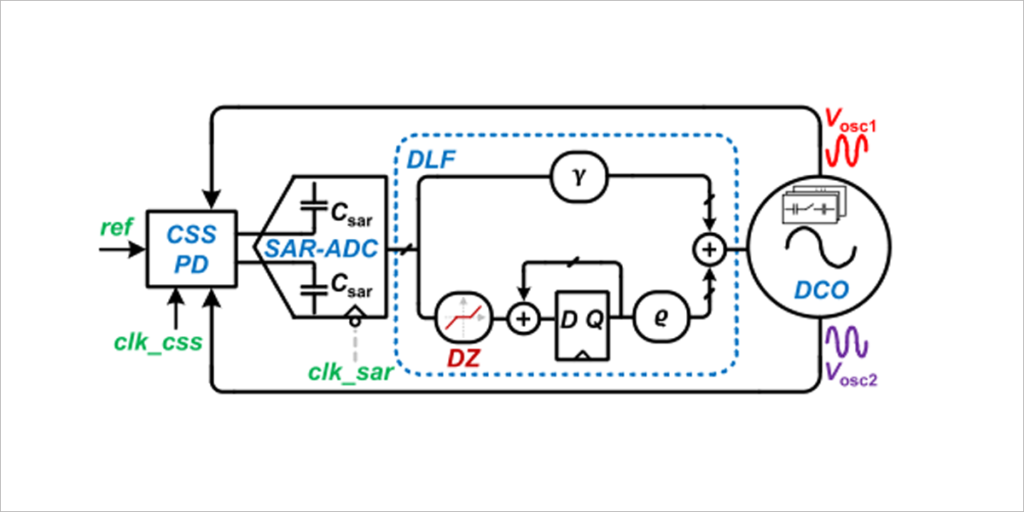

Estructura del chip CSS-ADPLL

El chip CSS-ADPLL cuenta con una estructura compacta que comprende un discriminador de timón de carga (CSS-PD), un SAR-ADC, un filtro digital, un convertidor de analógico a digital y un oscilador controlado numéricamente. Todo ello contribuye a un óptimo rendimiento de ruido de fase, una velocidad de bloqueo rápida y un consumo de energía mínimo.

Los resultados de la prueba demuestran que el chip ha logrado una fluctuación de reloj de 75,9 fs, un nivel de espuria de referencia de -50,13 dBc y un valor de figura de mérito (FoM) de -252,4 dB. Estos resultados lo ubican entre los bucles de enganche de fase digital que operan por encima de 20 GHz, con un área central del chip de solo 0,044 mm2.