Los investigadores del Instituto de Tecnología de Tokio (Tokyo Tech) han diseñado un transmisor de matriz en fase que supera los problemas comunes de la tecnología CMOS en la banda de 300 GHz. Este dispositivo, que destaca por su eficiencia de área, bajo consumo de energía y alta velocidad de datos, puede utilizarse en muchas aplicaciones tecnológicas en la banda de 300 GHz, como comunicaciones inalámbricas 6G, sensores de terahercios o radar, entre otras.

La mayoría de las frecuencias por encima de la marca de 250 GHz siguen sin asignar. En consecuencia, muchos investigadores están desarrollando transmisores/receptores de 300 GHz para aprovechar la baja absorción atmosférica en estas frecuencias, así como el potencial de velocidades de datos extremadamente altas que conlleva.

Sin embargo, las ondas electromagnéticas de alta frecuencia se debilitan rápidamente cuando viajan por el espacio libre. Para combatir este problema, los transmisores deben compensarlo logrando una gran potencia radiada efectiva.

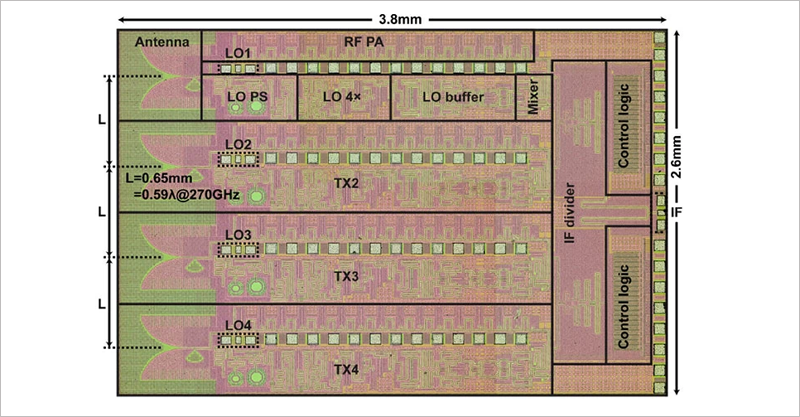

La solución propuesta por los investigadores de Tokyo Tech es un transmisor de matriz en fase compuesto por 64 elementos radiantes, que están dispuestos en 16 circuitos integrados con cuatro antenas cada uno. Dado que los elementos están dispuestos en tres dimensiones apilando placas de circuito impreso (PCB), este transmisor admite la dirección del haz 2D.

Gracias a esta disposición, la potencia transmitida se puede dirigir tanto vertical como horizontalmente, lo que permite una rápida dirección del haz y un seguimiento eficiente de los receptores. En particular, las antenas utilizadas son antenas Vivaldi, que pueden implementarse directamente en un chip y tienen una forma y un perfil de emisión adecuados para altas frecuencias.

Amplificación de la señal

Una característica importante del transmisor propuesto es su última arquitectura de amplificador de potencia (PA). Al colocar la etapa de amplificación justo antes de las antenas, el sistema sólo necesita amplificar las señales que ya han sido acondicionadas y procesadas. Esto conduce a una mayor eficiencia y un mejor rendimiento del amplificador.

Los investigadores también abordaron algunos problemas comunes que surgen con los diseños de transistores convencionales en procesos CMOS, como alta resistencia de puerta y grandes capacitancias parásitas. Optimizaron su diseño agregando caminos y vías de drenaje adicionales y alterando la geometría y la colocación de elementos entre las capas de metal.

Además de estas innovaciones, el equipo diseñó e implementó un amplificador de potencia de múltiples etapas de 300 GHz para usar con cada antena. Gracias a la excelente adaptación de impedancia entre etapas, los amplificadores demostraron un rendimiento excepcional.

Velocidad de datos de 108 Gb/s

Los investigadores probaron su diseño mediante simulaciones y experimentos, obteniendo resultados muy prometedores. El transmisor propuesto logró una velocidad de datos de 108 Gb/s en mediciones de sonda en PCB, que es sustancialmente más alta que la de otros transmisores de banda de 300 GHz de última generación.

Además, el transmisor también mostró una notable eficiencia de área en comparación con otros diseños basados en CMOS junto con un bajo consumo de energía, lo que destaca su potencial para aplicaciones miniaturizadas y con limitaciones de energía.