Los investigadores del Instituto de Tecnología de Tokio (Tokyo Tech) han desarrollado dos técnicas de diseño innovadoras que ayudan a minimizar las señales no deseadas, conocidas como espuelas fraccionarias, que afectan a los bucles bloqueados de fase (PLL) de N fraccional, utilizados en muchos sistemas de radar y transceptores inalámbricos modernos. Estos esfuerzos podrían abrir puertas a mejoras tecnológicas en comunicación inalámbrica, vigilancia y sistemas de seguimiento en la era 5G.

Muchas tecnologías emergentes y en evolución, como los sistemas de seguimiento de objetivos y los sensores remotos, dependen del funcionamiento de alta velocidad y sin errores de los sistemas de radar y transceptores de datos inalámbricos. En estas aplicaciones, los bucles de bloqueo de fase (PLL) son componentes que ayudan con la síntesis, modulación y sincronización de señales oscilantes. Por tanto, eliminar o minimizar las fuentes de error en los PLL es esencial para mejorar el rendimiento general de los sistemas.

El equipo de investigadores de Tokyo Tech ha desarrollado de dos técnicas de diseño innovadoras que conducen a un PLL de N fraccional de bajo estímulo. Los PLL de N fraccional son un tipo popular de PLL con óptima resolución y control flexible de frecuencia, aunque la fluctuación y los estímulos fraccionarios son los principales inconvenientes.

Técnicas propuestas

La primera técnica propuesta implica el uso de un divisor fraccionario en cascada. Este método implica dividir la palabra de control de frecuencia (FCW), una señal PLL interna que controla la frecuencia de salida, en dos, pero de manera que ambas estén lejos de ser un valor entero. La lógica subyacente es que, para los FCW de números enteros lejanos, las espuelas fraccionarias aparecen en el PLL en frecuencias más altas y los componentes de alta frecuencia se filtran naturalmente mediante las operaciones inherentes del PLL.

En particular, este enfoque no implica predistorsión digital (DPD), una técnica que introduce complejidad y provoca un bloqueo de fase más lento. La técnica de divisor en cascada propuesta logra un rendimiento de PLL sustancialmente mejorado al minimizar los estímulos fraccionarios.

La segunda técnica propuesta gira en torno a un DTC pseudodiferencial para evitar los problemas de las implementaciones de DTC estándar. En los diseños DTC convencionales, existen estrictas compensaciones entre la potencia del DTC, el rango de retardo, el ruido y el INL, lo que limita el nivel mínimo de estímulo fraccional alcanzable.

Para abordar este problema, los investigadores observaron que las no linealidades de los DTC contienen incluso componentes simétricos. En consecuencia, implementaron la función de un solo DTC utilizando dos DTC de medio rango con los mismos INL incluso simétricos en operación diferencial. Como resultado, estos INL se cancelaron naturalmente mediante resta en el detector de fase del PLL. El consumo total de energía del PLL propuesto es de sólo 8,89 mW con un suministro de 1 V, lo que lleva a una cifra de mérito de referencia de -247,4 dB.

Resultados de las pruebas

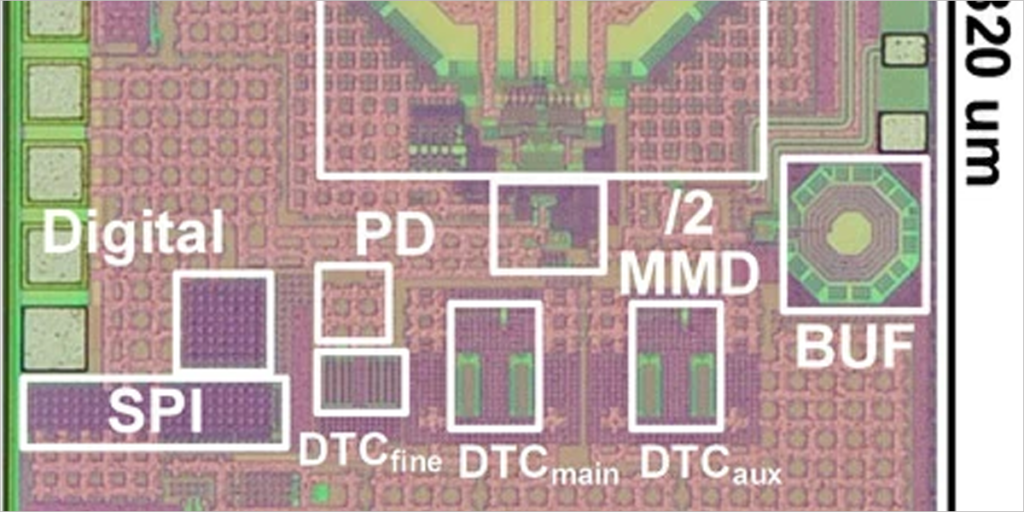

El equipo probó sus ideas implementando el PLL digital propuesto utilizando un proceso CMOS de 65 nm, que requiere un área de circuito activo de solo 0,23 mm2. Al comparar el rendimiento de su dispositivo con otros diseños de última generación, los investigadores observaron varias ventajas.

Al suprimir los estímulos fraccionarios, la fluctuación del PLL integrado se redujo de 243,5 fs a 143,7 fs, y gracias a las técnicas propuestas de DTC pseudodiferencial y divisor fraccionario en cascada, se logró la clase más baja de jitter sin tecnología DPD.