Debido a los crecientes costos de los nodos avanzados y las dificultades de reducir las señales de entrada-salida (IO) analógicas y de circuitos, las alternativas a las arquitecturas de un solo chip se están convirtiendo en un recurso principal. Los institutos de investigación CEA-Leti y CEA-List han presentado un interposer activo de componentes semiconductores complementarios de óxido metálico (CMOS), que integra administración de energía e interconexiones distribuidas para crear una innovadora jerarquía de memoria caché coherente y escalable.

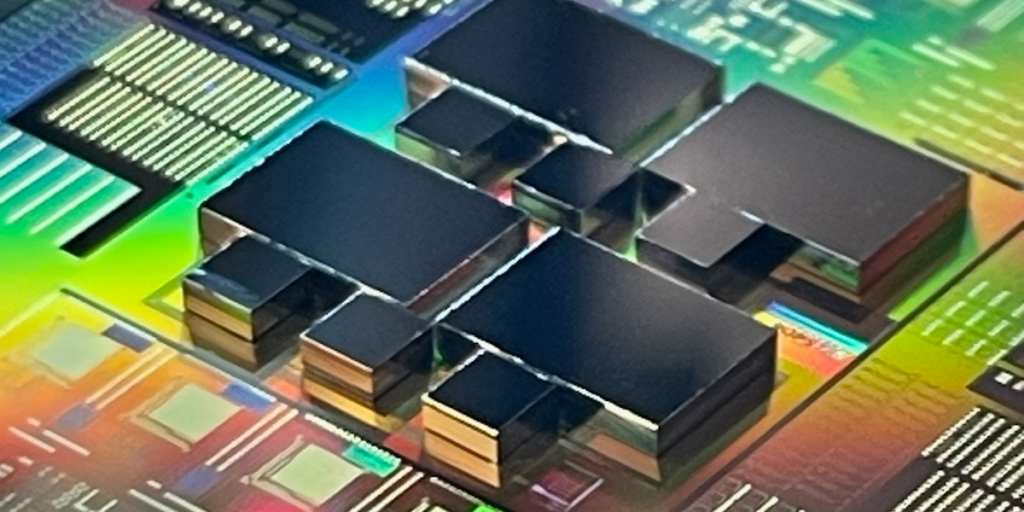

Los sistemas basados en chiplets que utilizan tecnologías 3D son compatibles con arquitecturas modulares escalables y con tecnología de partición basada en bloques de propiedad intelectual (IP) reutilizables. Además, las interconexiones 3D aumentan el ancho de banda de chip a chip y limitan el consumo general de energía. El concepto de chiplet sobre interposer implica la integración de una multiplicidad de chips en la misma plataforma de silicio; contrasta con las grandes plataformas monolíticas de sistemas en chip (SoC).

Tecnología de red óptica en chip

En la demostración de CEA-Leti, se apilaron en 3D seis chiplets FD-SOI de 28 nm en un intercalador activo en un proceso de 65 nm, para crear un total de 96 núcleos. Para mejorar aún más la transmisión de datos durante la comunicación, los investigadores están contribuyendo al desarrollo de un enfoque disruptivo para la informática de alto rendimiento (HPC): la tecnología de red óptica en chip (ONoC).

Los fotones (luz) tienen el potencial de ofrecer una comunicación rápida en el chip para HPC, con mayor ancho de banda y menor consumo de energía. Los principales desafíos tecnológicos que enfrentó su visión arquitectónica de un enfoque ONoC para los chiplets fueron una interfaz escalable y de bajo perfil entre los chiplets y la red; un enrutamiento descentralizado para reducir el movimiento de datos dentro del sistema; una gestión térmica compatible con comunicaciones ópticas; y mantener el rendimiento de los chiplets individuales en integraciones de múltiples chipsets.

Creación de vías a través de silicio

Al abordar los problemas mencionados anteriormente, los investigadores cointegraron con éxito interconexiones 3D y dispositivos fotónicos utilizando un enfoque recientemente demostrado para formar vías a través de silicio (TSV) de 10 µm de diámetro por 100 µm de alto a través de la metalización de cobre dentro de un chip fotónico. Se mejoró el aislamiento térmico grabando cavidades traseras de 40 µm de diámetro debajo de los microanillos ópticos, lo que condujo a una reducción del 70% en la potencia necesaria para sintonizar los microanillos. Además, han demostrado una gestión termomecánica eficiente de la tensión del intercalador fotónico adelgazado de 100 µm para procesos de ensamblaje.

Estos ajustes fueron obligatorios para el ensamblaje de las matrices superiores del demostrador del interposer fotónico Popstar, que alberga cuatro chips de cálculo y seis chips controladores electroópticos. La exitosa integración de TSV en este intercalador fotónico se demostró mediante la evaluación de los rendimientos eléctricos y el rendimiento electroóptico de las cadenas TSV.

Al combinar la integración 3D con TSV de proceso intermedio y empaquetado avanzado, basado en chips invertidos de paso pequeño y conexión de fibra óptica, se logró la integración heterogénea de un dispositivo fotónico en un intercalador de silicio.