El Instituto Nacional de Tecnología de la Información y las Comunicaciones (NICT), la Universidad de Hiroshima (Japón) y la compañía THine Electronics han desarrollado una tecnología de transmisión inalámbrica de modificación por cambio de fase cuaternaria (QPSK) de 20 Gb/s mediante el uso de la tecnología demoduladora de banda base de señal mixta. Esta innovación proporcionaría una gran ventaja para lograr una transmisión de datos inalámbrica con mayor eficiencia energética para aplicaciones de mayor velocidad.

Los resultados de esta investigación allanan el camino para implementaciones prácticas de circuitos mediante arquitecturas de señal mixta para diversas aplicaciones que requieren un mayor rendimiento y una mayor eficiencia energética. La arquitectura de señal mixta logra una transmisión de datos de velocidad ultraalta, lo que mejora la eficiencia energética.

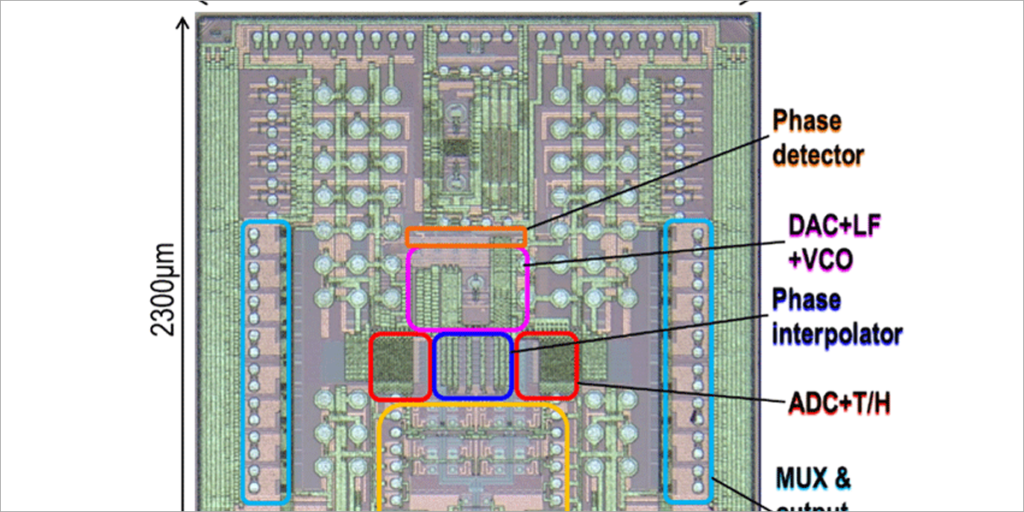

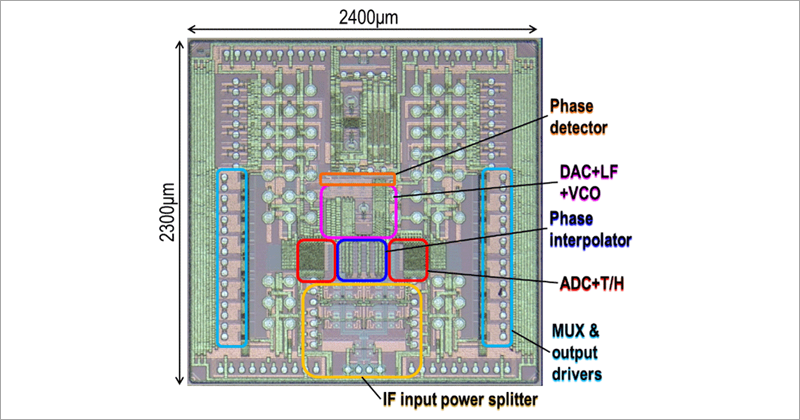

El grupo de investigación ha desarrollado un circuito demodulador de banda base de señal mixta que consta de un conversor analógico a digital (ADC) de alta velocidad y baja resolución, y un procesador de señal digital (DSP) de pequeña escala.

Si se utilizan para tales comunicaciones de alta velocidad, el rendimiento requerido de ADC y DSP da como resultado una distorsión extrema de eficiencia energética. Se espera que esta tecnología realice comunicaciones de datos de mayor velocidad que superen las decenas de Gb/s, logrando un circuito demodulador de banda base con eficiencia energética superior.

Transmisión de datos de señales moduladas QPSK de 20 Gb/s

Los circuitos receptores desarrollados, el demodulador de banda base y los arreglos de compuertas lógicas programables en sitio (FPGA) con circuitos lógicos han logrado la transmisión de datos de señales moduladas QPSK de 20 Gb/s. Las funciones implementadas en FPGA se integrarán en circuitos receptores de banda base en su aplicación práctica.

La tecnología lograda simplifica los circuitos al hacer que la frecuencia portadora sea un múltiplo entero de la frecuencia portadora del símbolo, logrando una transmisión de datos de ultraalta velocidad mediante una configuración de circuito única con un bucle QPSK de señal mixta que integra frecuencia portadora, temporización y recuperación de datos y funciones.

Como resultado, el grupo de investigación ha logrado el conversor analógico a digital de alta velocidad y baja resolución implementando un ADC de 3 bits entrelazado de ocho vías (aceleración ocho veces mayor que el total de circuitos) con una frecuencia de muestreo de 40 gigamuestras por segundo (40 Gb/s) y datos recuperados con la FPGA.